produk Kategori

- Pemancar FM

- 0-50w 50w-1000w 2kw-10kw 10kw +

- Pemancar TV

- 0-50w 50-1kw 2kw-10kw

- FM antena

- TV Antenna

- antena aksesori

- Kabel penyambung Power Splitter Beban dummy

- RF Transistor

- Bekalan kuasa

- Peralatan Audio

- DTV Front End Equipment

- Sistem link

- sistem STL sistem Link Microwave

- Radio FM

- Meter kuasa

- Produk-produk lain

- Khas untuk Coronavirus

produk Tags

Tapak Fmuser

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Orang Afrika

- sq.fmuser.net -> Bahasa Albania

- ar.fmuser.net -> Bahasa Arab

- hy.fmuser.net -> Armenia

- az.fmuser.net -> Azerbaijan

- eu.fmuser.net -> Basque

- be.fmuser.net -> Belarus

- bg.fmuser.net -> Bulgaria

- ca.fmuser.net -> Bahasa Catalan

- zh-CN.fmuser.net -> Bahasa Cina (Ringkas)

- zh-TW.fmuser.net -> Bahasa Cina (Tradisional)

- hr.fmuser.net -> Bahasa Croatia

- cs.fmuser.net -> Bahasa Czech

- da.fmuser.net -> Denmark

- nl.fmuser.net -> Belanda

- et.fmuser.net -> Estonia

- tl.fmuser.net -> Orang Filipina

- fi.fmuser.net -> Bahasa Finland

- fr.fmuser.net -> Bahasa Perancis

- gl.fmuser.net -> orang Galicia

- ka.fmuser.net -> Orang Georgia

- de.fmuser.net -> Jerman

- el.fmuser.net -> Greek

- ht.fmuser.net -> Haitian Creole

- iw.fmuser.net -> Bahasa Ibrani

- hi.fmuser.net -> Bahasa Hindi

- hu.fmuser.net -> Bahasa Hungary

- is.fmuser.net -> Bahasa Iceland

- id.fmuser.net -> Bahasa Indonesia

- ga.fmuser.net -> Ireland

- it.fmuser.net -> Bahasa Itali

- ja.fmuser.net -> Jepun

- ko.fmuser.net -> Bahasa Korea

- lv.fmuser.net -> Bahasa Latvia

- lt.fmuser.net -> Bahasa Lithuania

- mk.fmuser.net -> orang Macedonia

- ms.fmuser.net -> Bahasa Melayu

- mt.fmuser.net -> Malta

- no.fmuser.net -> Bahasa Norway

- fa.fmuser.net -> Parsi

- pl.fmuser.net -> Bahasa Poland

- pt.fmuser.net -> Portugis

- ro.fmuser.net -> Romania

- ru.fmuser.net -> Rusia

- sr.fmuser.net -> Bahasa Serbia

- sk.fmuser.net -> Bahasa Slovak

- sl.fmuser.net -> Bahasa Slovenia

- es.fmuser.net -> Sepanyol

- sw.fmuser.net -> Swahili

- sv.fmuser.net -> Sweden

- th.fmuser.net -> Thai

- tr.fmuser.net -> Turki

- uk.fmuser.net -> Ukraine

- ur.fmuser.net -> Bahasa Urdu

- vi.fmuser.net -> Vietnam

- cy.fmuser.net -> Wales

- yi.fmuser.net -> Bahasa Yiddish

Transistor PMOS dan NMOS

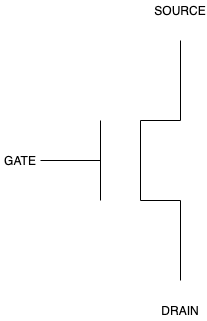

Mikropemproses dibina daripada transistor. Khususnya, ia dibina daripada transistor MOS. MOS ialah akronim untuk Metal-Oxide Semiconductor. Terdapat dua jenis transistor MOS: pMOS (positif-MOS) dan nMOS (negatif-MOS). Setiap pMOS dan nMOS dilengkapi dengan tiga komponen utama: pintu pagar, punca dan longkang.

Untuk memahami dengan betul cara pMOS dan nMOS beroperasi, adalah penting untuk mentakrifkan beberapa istilah dahulu:

litar tertutup: Ini bermakna bahawa elektrik mengalir dari pintu masuk ke punca.

litar terbuka: Ini bermakna elektrik tidak mengalir dari pintu masuk ke punca; tetapi sebaliknya, elektrik mengalir dari pintu masuk ke longkang.

Apabila transistor nMOS menerima voltan yang tidak boleh diabaikan, sambungan dari punca ke longkang bertindak sebagai wayar. Elektrik akan mengalir dari punca ke longkang tanpa halangan — ini dirujuk sebagai litar tertutup. Sebaliknya, apabila transistor nMOS menerima voltan pada sekitar 0 volt, sambungan dari punca ke longkang akan terputus dan ini dirujuk sebagai litar terbuka.

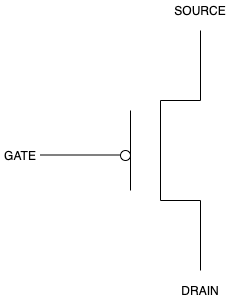

Transistor jenis-p berfungsi betul-betul bertentangan dengan transistor jenis-n. Manakala nMOS akan membentuk litar tertutup dengan punca apabila voltan tidak boleh diabaikan, pMOS akan membentuk litar terbuka dengan punca apabila voltan tidak boleh diabaikan.

Seperti yang anda boleh lihat dalam imej transistor pMOS yang ditunjukkan di atas, satu-satunya perbezaan antara transistor pMOS dan transistor nMOS ialah bulatan kecil antara pintu gerbang dan bar pertama. Bulatan ini menyongsangkan nilai daripada voltan; jadi, jika get menghantar wakil voltan nilai 1, maka penyongsang akan menukar 1 kepada 0 dan menyebabkan litar berfungsi dengan sewajarnya.

Memandangkan pMOS dan nMOS berfungsi dengan cara yang bertentangan — dengan cara yang saling melengkapi — apabila kita menggabungkan kedua-duanya menjadi satu litar MOS gergasi, ia dipanggil litar cMOS, yang bermaksud semikonduktor logam-oksida pelengkap.

Menggunakan Litar MOS

Kita boleh menggabungkan litar pMOS dan nMOS untuk membina struktur yang lebih kompleks yang dipanggil GATES, lebih khusus: get logik. Kami telah pun memperkenalkan konsep fungsi logik ini dan jadual kebenaran yang berkaitan dalam blog sebelumnya, yang boleh anda temui dengan mengklik disini.

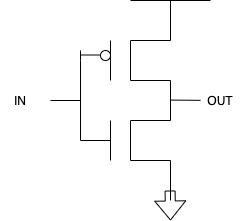

Kita boleh melampirkan transistor pMOS yang bersambung ke sumber dan transistor nMOS yang bersambung ke tanah. Ini akan menjadi contoh pertama transistor cMOS kami.

Transistor cMOS ini bertindak dengan cara yang serupa dengan fungsi logik NOT.

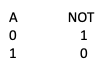

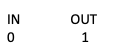

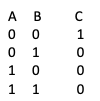

Mari kita lihat jadual NOT truth:

Dalam jadual kebenaran NOT, setiap nilai input: A adalah terbalik. Apakah yang berlaku dengan litar di atas?

Baiklah, mari bayangkan inputnya ialah 0.

0 masuk dan pergi ke atas dan ke bawah wayar ke kedua-dua pMOS (atas) dan nMOS (bawah). Apabila nilai 0 mencapai pMOS, ia akan terbalik kepada 1; jadi, sambungan kepada sumber ditutup. Ini akan menghasilkan nilai logik 1 selagi sambungan ke tanah (longkang) tidak juga ditutup. Nah, kerana transistor adalah pelengkap, kita tahu bahawa transistor nMOS tidak akan menyongsangkan nilai; jadi, ia mengambil nilai 0 sebagaimana adanya dan akan — oleh itu — mencipta litar terbuka ke tanah (longkang). Oleh itu, nilai logik 1 dihasilkan untuk get.

Apakah yang berlaku jika 1 ialah nilai IN? Nah, mengikut langkah yang sama seperti di atas, nilai 1 akan dihantar ke kedua-dua pMOS dan nMOS. Apabila nilai diterima oleh pMOS, nilai akan terbalik kepada 0; oleh itu, sambungan kepada SUMBER terbuka. Apabila nilai diterima oleh nMOS, nilai tidak akan terbalik; oleh itu, nilai kekal 1. Apabila nilai 1 diterima oleh nMOS, sambungan ditutup; jadi, sambungan ke tanah ditutup. Ini akan menghasilkan nilai logik 0.

Menyatukan dua set input/output menghasilkan:

Agak mudah untuk melihat bahawa jadual kebenaran ini adalah sama seperti yang TIDAK dihasilkan oleh fungsi logik. Oleh itu, ini dikenali sebagai gerbang NOT.

Bolehkah kita menggunakan dua transistor mudah ini untuk membuat struktur yang lebih rumit? betul-betul! Seterusnya, kita akan membina gerbang NOR dan gerbang OR.

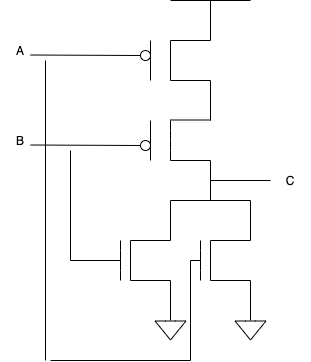

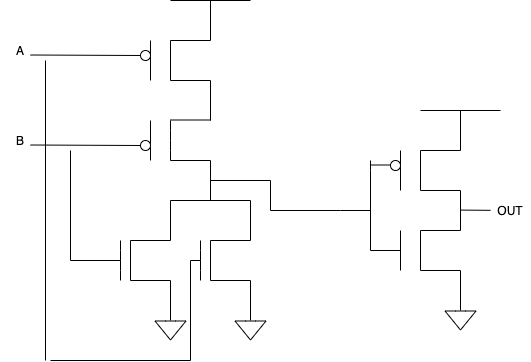

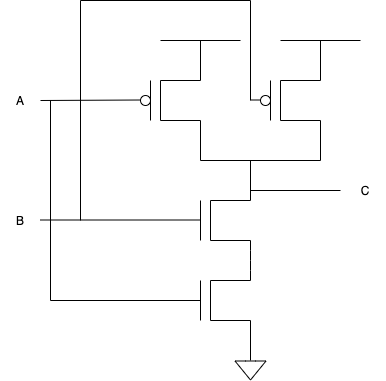

Litar ini menggunakan dua transistor pMOS di bahagian atas dan dua transistor nMOS di bahagian bawah. Sekali lagi, mari kita lihat input ke pintu pagar untuk melihat bagaimana ia berkelakuan.

Apabila A ialah 0 dan B ialah 0, get ini akan menyongsangkan kedua-dua nilai kepada 1 apabila ia mencapai transistor pMOS; walau bagaimanapun, transistor nMOS kedua-duanya akan mengekalkan nilai 0. Ini akan membawa get untuk menghasilkan nilai 1.

Apabila A ialah 0 dan B ialah 1, get ini akan menyongsangkan kedua-dua nilai apabila ia mencapai transistor pMOS; jadi, A akan bertukar kepada 1 dan B akan bertukar kepada 0. Ini tidak akan membawa kepada sumber; kerana kedua-dua transistor memerlukan litar tertutup untuk menyambungkan input kepada sumber. Transistor nMOS tidak menyongsangkan nilai; jadi, nMOS yang dikaitkan dengan A akan menghasilkan 0, dan nMOS yang dikaitkan dengan B akan menghasilkan 1; oleh itu, nMOS yang dikaitkan dengan B akan menghasilkan litar tertutup ke tanah. Ini akan membawa gerbang untuk menghasilkan nilai 0.

Apabila A ialah 1 dan B ialah 0, get ini akan menyongsangkan kedua-dua nilai apabila ia mencapai transistor pMOS; jadi, A akan bertukar kepada 0dan B akan bertukar kepada 1. Ini tidak akan membawa kepada sumber; kerana kedua-dua transistor memerlukan litar tertutup untuk menyambungkan input kepada sumber. Transistor nMOS tidak menyongsangkan nilai; jadi, nMOS yang dikaitkan dengan A akan menghasilkan 1, dan nMOS yang dikaitkan dengan B akan menghasilkan 0; oleh itu, nMOS yang dikaitkan dengan Awill menghasilkan litar tertutup ke tanah. Ini akan membawa gerbang untuk menghasilkan nilai 0.

Apabila A ialah 1 dan B ialah 1, get ini akan menyongsangkan kedua-dua nilai apabila ia mencapai transistor pMOS; jadi, A akan bertukar kepada 0 dan B akan bertukar kepada 0. Ini tidak akan membawa kepada sumber; kerana kedua-dua transistor memerlukan litar tertutup untuk menyambungkan input kepada sumber. Transistor nMOS tidak menyongsangkan nilai; jadi, nMOS yang dikaitkan dengan A akan menghasilkan 1, dan nMOS yang dikaitkan dengan B akan menghasilkan 1; oleh itu, nMOS yang dikaitkan dengan A dan nMOS yang dikaitkan dengan B akan menghasilkan litar tertutup ke tanah. Ini akan membawa gerbang untuk menghasilkan nilai 0.

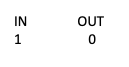

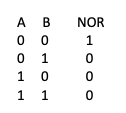

Oleh itu, jadual kebenaran gerbang adalah seperti berikut:

Sementara itu, jadual kebenaran fungsi logik NOR adalah seperti berikut:

Oleh itu, kami telah mengesahkan bahawa get ini ialah get NOR kerana ia berkongsi jadual kebenarannya dengan fungsi logik NOR.

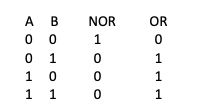

Sekarang, kita akan meletakkan kedua-dua gerbang, yang telah kita buat setakat ini, bersama-sama untuk menghasilkan gerbang ATAU. Ingat, NOR bermaksud NOT OR; jadi, jika kita terbalikkan gerbang yang sudah terbalik, kita akan mendapatkan semula yang asal. Mari kita uji ini untuk melihatnya dalam tindakan.

Apa yang telah kami lakukan di sini ialah kami telah mengambil get NOR dari sebelumnya dan menggunakan get NOT pada output. Seperti yang telah kami tunjukkan di atas, get NOT akan mengambil nilai 1 dan mengeluarkan 0, dan get NOT akan mengambil nilai 0 dan mengeluarkan 1.

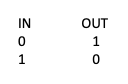

Ini akan mengambil nilai get NOR dan menukar semua 0s kepada 1s dan 1s kepada 0s. Oleh itu, jadual kebenaran adalah seperti berikut:

Jika anda ingin lebih banyak latihan menguji gerbang ini, jangan ragu untuk mencuba nilai di atas untuk diri sendiri dan lihat bahawa pintu itu menghasilkan keputusan yang setara!

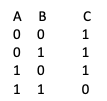

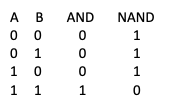

Saya mendakwa ini ialah get NAND, tetapi mari kita uji jadual kebenaran get ini untuk menentukan sama ada ia benar-benar get NAND.

Apabila A ialah 0 dan B ialah 0, pMOS A akan menghasilkan 1, dan nMOS A akan menghasilkan 0; Oleh itu, get ini akan menghasilkan logik 1 kerana ia disambungkan kepada punca dengan litar tertutup dan terputus dari tanah dengan litar terbuka.

Apabila A ialah 0 dan B ialah 1, pMOS A akan menghasilkan 1, dan nMOS A akan menghasilkan 0; Oleh itu, get ini akan menghasilkan logik 1 kerana ia disambungkan kepada punca dengan litar tertutup dan terputus dari tanah dengan litar terbuka.

Apabila A ialah 1 dan B ialah 0, pMOS B akan menghasilkan 1, dan nMOS B akan menghasilkan 0; Oleh itu, get ini akan menghasilkan logik 1 kerana ia disambungkan kepada punca dengan litar tertutup dan terputus dari tanah dengan litar terbuka.

Apabila A ialah 1 dan B ialah 1, pMOS A akan menghasilkan 0, dan nMOS A akan menghasilkan 1; jadi, kita mesti menyemak pMOS dan nMOS B juga. pMOS B akan menghasilkan 0, dan nMOS B akan menghasilkan 1; Oleh itu, get ini akan menghasilkan logik 0 kerana ia diputuskan dari punca dengan litar terbuka dan disambungkan ke tanah dengan litar tertutup.

Jadual kebenaran adalah seperti berikut:

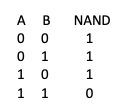

Sementara itu, jadual kebenaran fungsi logik NAND adalah seperti berikut:

Oleh itu, kami telah mengesahkan bahawa ini sebenarnya adalah gerbang NAND.

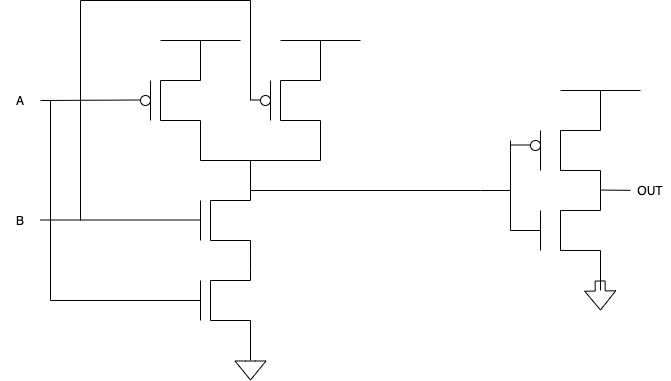

Sekarang, bagaimana kita membina gerbang DAN? Nah, kita akan membina get AND dengan cara yang sama seperti kita membina get OR daripada get NOR! Kami akan memasang penyongsang!

Oleh kerana semua yang telah kita lakukan menggunakan fungsi NOT pada output get NAND, jadual kebenaran akan kelihatan seperti ini:

Sekali lagi, sila sahkan untuk memastikan bahawa apa yang saya beritahu anda adalah benar.

Hari ini, kami telah membincangkan apa itu transistor pMOS dan nMOS serta cara menggunakannya untuk membina struktur yang lebih kompleks! Saya harap anda mendapati blog ini bermaklumat. Jika anda ingin membaca blog saya sebelum ini, anda akan dapati senarai di bawah.