produk Kategori

- Pemancar FM

- 0-50w 50w-1000w 2kw-10kw 10kw +

- Pemancar TV

- 0-50w 50-1kw 2kw-10kw

- FM antena

- TV Antenna

- antena aksesori

- Kabel penyambung Power Splitter Beban dummy

- RF Transistor

- Bekalan kuasa

- Peralatan Audio

- DTV Front End Equipment

- Sistem link

- sistem STL sistem Link Microwave

- Radio FM

- Meter kuasa

- Produk-produk lain

- Khas untuk Coronavirus

produk Tags

Tapak Fmuser

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Orang Afrika

- sq.fmuser.net -> Bahasa Albania

- ar.fmuser.net -> Bahasa Arab

- hy.fmuser.net -> Armenia

- az.fmuser.net -> Azerbaijan

- eu.fmuser.net -> Basque

- be.fmuser.net -> Belarus

- bg.fmuser.net -> Bulgaria

- ca.fmuser.net -> Bahasa Catalan

- zh-CN.fmuser.net -> Bahasa Cina (Ringkas)

- zh-TW.fmuser.net -> Bahasa Cina (Tradisional)

- hr.fmuser.net -> Bahasa Croatia

- cs.fmuser.net -> Bahasa Czech

- da.fmuser.net -> Denmark

- nl.fmuser.net -> Belanda

- et.fmuser.net -> Estonia

- tl.fmuser.net -> Orang Filipina

- fi.fmuser.net -> Bahasa Finland

- fr.fmuser.net -> Bahasa Perancis

- gl.fmuser.net -> orang Galicia

- ka.fmuser.net -> Orang Georgia

- de.fmuser.net -> Jerman

- el.fmuser.net -> Greek

- ht.fmuser.net -> Haitian Creole

- iw.fmuser.net -> Bahasa Ibrani

- hi.fmuser.net -> Bahasa Hindi

- hu.fmuser.net -> Bahasa Hungary

- is.fmuser.net -> Bahasa Iceland

- id.fmuser.net -> Bahasa Indonesia

- ga.fmuser.net -> Ireland

- it.fmuser.net -> Bahasa Itali

- ja.fmuser.net -> Jepun

- ko.fmuser.net -> Bahasa Korea

- lv.fmuser.net -> Bahasa Latvia

- lt.fmuser.net -> Bahasa Lithuania

- mk.fmuser.net -> orang Macedonia

- ms.fmuser.net -> Bahasa Melayu

- mt.fmuser.net -> Malta

- no.fmuser.net -> Bahasa Norway

- fa.fmuser.net -> Parsi

- pl.fmuser.net -> Bahasa Poland

- pt.fmuser.net -> Portugis

- ro.fmuser.net -> Romania

- ru.fmuser.net -> Rusia

- sr.fmuser.net -> Bahasa Serbia

- sk.fmuser.net -> Bahasa Slovak

- sl.fmuser.net -> Bahasa Slovenia

- es.fmuser.net -> Sepanyol

- sw.fmuser.net -> Swahili

- sv.fmuser.net -> Sweden

- th.fmuser.net -> Thai

- tr.fmuser.net -> Turki

- uk.fmuser.net -> Ukraine

- ur.fmuser.net -> Bahasa Urdu

- vi.fmuser.net -> Vietnam

- cy.fmuser.net -> Wales

- yi.fmuser.net -> Bahasa Yiddish

Apa itu Half Subtractor: Working and Applications, K-MAP, Circuit menggunakan NAND Gate

Date:2021/10/18 21:55:58 Hits:

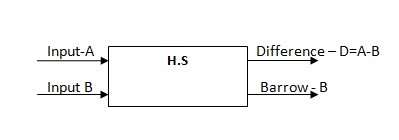

Untuk memproses maklumat seperti cahaya atau suara dari satu titik ke titik yang lain, kita dapat menggunakan litar analog dengan memberikan input yang tepat dalam bentuk isyarat analog. Dalam proses ini, ada kemungkinan kebisingan dipungut oleh isyarat analog input dan ini boleh menyebabkan kehilangan sinyal output, ini bermaksud apa pun input yang kita proses pada tahap input tidak sama dengan tahap output. Untuk, mengatasi litar digital ini dilaksanakan. Litar digital boleh direka dengan pintu logik. Gerbang logik adalah litar elektronik yang melakukan operasi logik berdasarkan inputnya dan memberikan output hanya satu bit, sama ada rendah (Logik 0 = voltan sifar) atau tinggi (Logik 1 = voltan tinggi). Litar gabungan dapat dirancang dengan lebih daripada satu pintu logik. Litar ini cepat dan tidak bergantung pada masa tanpa maklum balas antara input dan output. Litar gabungan berguna untuk operasi aritmetik dan Boolean. Contoh terbaik litar kombinasi termasuk Half adder, full adder, half Subtractor, full subtractor, multiplexer, demultiplexers, encoder, and decoder. Apa itu Half Subtractor? Half Subtractor seperti yang disebutkan di atas adalah litar gabungan dan seperti namanya digunakan untuk mengurangkan dua bit dari input. Di sini output subtraktor sepenuhnya bergantung pada input sekarang dan tidak bergantung pada tahap sebelumnya. Keluaran separuh pengurangan adalah perbezaan dan penghadang. Ia sama dengan pengurangan arthimetic di mana jika subtrahend lebih besar daripada minuend kita akan meminjam B = 1 atau jika tidak, pinjaman akan tetap sifar B = 0. Untuk memahaminya dengan lebih baik mari masuk ke dalam jadual kebenaran yang ditunjukkan di bawah.  half-subtractor-block-diagram Jadual Kebenaran Jadual kebenaran setengah-subtraktor menunjukkan nilai output mengikut input yang diterapkan pada peringkat input. Jadual kebenaran terbahagi kepada dua bahagian. Bahagian kiri dilambangkan sebagai tahap input dan bahagian kanan dilambangkan sebagai tahap output. Dalam litar digital, input 0 dan input 1 menunjukkan logik rendah dan tinggi logik. Mengikut konfigurasi, logik rendah bermaksud voltan sifar, logik tinggi bermaksud voltan tinggi (seperti 5V, 7V, 12V dll). Input OutputsInput - AInput - BDifference -DBarrow - B 000010 1001111100Truth Table ExplanationApabila input A dan B adalah sifar output setengah subtraktor D dan B juga sifar. Apabila input A tinggi dan B adalah sifar maka perbezaannya adalah tinggi iaitu, 1 dan 1 Barrow adalah sifar Apabila input A adalah sifar dan input B tinggi, maka output D dan B tinggi dengan masing-masing. Apabila kedua-dua input tinggi, kedua-dua output setengah-pengurang adalah sifar. Dari jadual kebenaran di atas, kita dapat cari persamaan untuk Perbezaan (D) dan Barrow (B) .Perolehan untuk Perbezaan-D: Perbezaan tinggi apabila input A = 0, B = 0 dan A = 1, B = XNUMX. Dari pernyataan ini D = AB '+ A'B = A⊕B. Sesuai dengan persamaan D ia menunjukkan Ex-atau gate.D = A⊕BEquations for Barrow-B: Barro hanya tinggi apabila input A rendah dan B tinggi. Dari sudut ini, persamaan untuk Barrow B akan menjadi, B = A'BB = A'BDaripada perbezaan di atas dan persamaan barrow, kita dapat merancang rajah litar separuh-pengurang menggunakan peta K -MapK - MapKarnaugh mempermudah ungkapan algebra Boolean untuk litar separuh Penolak. Ini adalah kaedah rasmi untuk mencari persamaan algebra Boolean untuk mana-mana litar. Mari selesaikan ungkapan Boolean untuk litar setengah-pengurangan menggunakan peta K-peta. K-Map for Difference (D) dan Barrow (B)

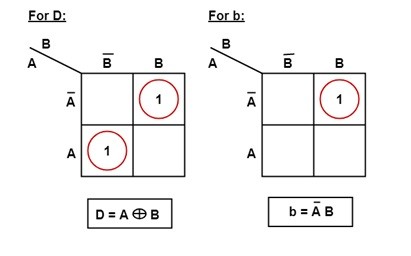

half-subtractor-block-diagram Jadual Kebenaran Jadual kebenaran setengah-subtraktor menunjukkan nilai output mengikut input yang diterapkan pada peringkat input. Jadual kebenaran terbahagi kepada dua bahagian. Bahagian kiri dilambangkan sebagai tahap input dan bahagian kanan dilambangkan sebagai tahap output. Dalam litar digital, input 0 dan input 1 menunjukkan logik rendah dan tinggi logik. Mengikut konfigurasi, logik rendah bermaksud voltan sifar, logik tinggi bermaksud voltan tinggi (seperti 5V, 7V, 12V dll). Input OutputsInput - AInput - BDifference -DBarrow - B 000010 1001111100Truth Table ExplanationApabila input A dan B adalah sifar output setengah subtraktor D dan B juga sifar. Apabila input A tinggi dan B adalah sifar maka perbezaannya adalah tinggi iaitu, 1 dan 1 Barrow adalah sifar Apabila input A adalah sifar dan input B tinggi, maka output D dan B tinggi dengan masing-masing. Apabila kedua-dua input tinggi, kedua-dua output setengah-pengurang adalah sifar. Dari jadual kebenaran di atas, kita dapat cari persamaan untuk Perbezaan (D) dan Barrow (B) .Perolehan untuk Perbezaan-D: Perbezaan tinggi apabila input A = 0, B = 0 dan A = 1, B = XNUMX. Dari pernyataan ini D = AB '+ A'B = A⊕B. Sesuai dengan persamaan D ia menunjukkan Ex-atau gate.D = A⊕BEquations for Barrow-B: Barro hanya tinggi apabila input A rendah dan B tinggi. Dari sudut ini, persamaan untuk Barrow B akan menjadi, B = A'BB = A'BDaripada perbezaan di atas dan persamaan barrow, kita dapat merancang rajah litar separuh-pengurang menggunakan peta K -MapK - MapKarnaugh mempermudah ungkapan algebra Boolean untuk litar separuh Penolak. Ini adalah kaedah rasmi untuk mencari persamaan algebra Boolean untuk mana-mana litar. Mari selesaikan ungkapan Boolean untuk litar setengah-pengurangan menggunakan peta K-peta. K-Map for Difference (D) dan Barrow (B) K-peta untuk Perbezaan (D) dan Barrow (B) Menurut K-peta implan pertama adalah A'B dan implan kedua adalah AB'. Apabila kita menyederhanakan kedua persamaan implan ini, akan mendapat persamaan yang dipermudahkan untuk Perbezaan DD = A'B + AB'Kemudian, D = A⊕B. Persamaan ini hanya menunjukkan pintu Ex-OR. Untuk mencari ungkapan Boolean yang dipermudah untuk barrow B, kita perlu mengikuti proses yang sama yang kita ikuti untuk Difference D. Oleh itu, B = A'B.Half Subtractor menggunakan gerbang NAND GatesNAND dan Gerbang NOR dipanggil gerbang sejagat. Di sini, gerbang NAND disebut gerbang sejagat kerana kita dapat merancang apa-apa jenis litar digital dengan menggunakan kombinasi nombor n gerbang NAND. Kerana keistimewaan ini, gerbang NAND disebut sebagai gerbang sejagat. Sekarang, kami merancang litar setengah-Subtraktor menggunakan gerbang NAND.

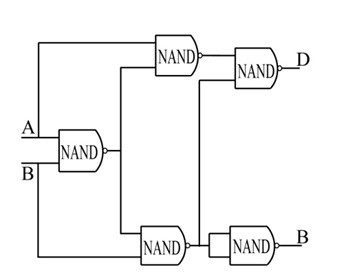

K-peta untuk Perbezaan (D) dan Barrow (B) Menurut K-peta implan pertama adalah A'B dan implan kedua adalah AB'. Apabila kita menyederhanakan kedua persamaan implan ini, akan mendapat persamaan yang dipermudahkan untuk Perbezaan DD = A'B + AB'Kemudian, D = A⊕B. Persamaan ini hanya menunjukkan pintu Ex-OR. Untuk mencari ungkapan Boolean yang dipermudah untuk barrow B, kita perlu mengikuti proses yang sama yang kita ikuti untuk Difference D. Oleh itu, B = A'B.Half Subtractor menggunakan gerbang NAND GatesNAND dan Gerbang NOR dipanggil gerbang sejagat. Di sini, gerbang NAND disebut gerbang sejagat kerana kita dapat merancang apa-apa jenis litar digital dengan menggunakan kombinasi nombor n gerbang NAND. Kerana keistimewaan ini, gerbang NAND disebut sebagai gerbang sejagat. Sekarang, kami merancang litar setengah-Subtraktor menggunakan gerbang NAND. setengah-subtraktor yang dilaksanakan-dengan-NAND-gerbangKita boleh merancang litar setengah-sub-traktor dengan lima gerbang NAND. Pertimbangkan A dan B sebagai input ke tahap pertama gerbang NAND, outputnya kembali disambungkan sebagai satu input ke gerbang NAND kedua serta gerbang NAND ketiga. Mengikut input mereka, ia memberikan output dan pada peringkat akhir dari gerbang NAND, perbezaan output D dan output barrow B akan berada pada keluaran mereka. Perbezaan akhir persamaan output D adalah D = A EquB dan persamaan barrow B sebagai B = A'B. Dengan menggunakan kombinasi gerbang NAND yang berbeza untuk membina separuh-pengurang, persamaan perbezaan dan barrow terakhir adalah D = A⊕B dan B = A'B sahaja. Half Subtractor Terdapat pelbagai aplikasi subtraktor ini. Secara praktikal mereka mudah dianalisis. Sebilangan daripadanya disenaraikan seperti berikut. Untuk mengurangkan nombor yang terdapat pada kedudukan paling sedikit pada lajur, pengurang ini lebih disukai. Unit Aritmetik dan Logik (ALU) yang ada dalam pemproses lebih suka unit ini untuk pengurangan. Untuk mengurangkan gangguan pada suara ini digunakan. Berdasarkan operasi yang diperlukan, setengah pengurang mempunyai keupayaan untuk meningkatkan atau mengurangkan bilangan pengendali. Separuh pengurang digunakan dalam penguat. Semasa menghantar isyarat audio, ini digunakan untuk mengelakkan penyelewengan. Oleh itu, ini semua mengenai Litar pengurangan separuh. Dalam keadaan masa nyata mengurangkan beberapa bilangan bit tidak dapat dilakukan dengan menggunakan separuh pengurang. Kekurangan ini dapat diatasi dengan menggunakan Penolak penuh.

setengah-subtraktor yang dilaksanakan-dengan-NAND-gerbangKita boleh merancang litar setengah-sub-traktor dengan lima gerbang NAND. Pertimbangkan A dan B sebagai input ke tahap pertama gerbang NAND, outputnya kembali disambungkan sebagai satu input ke gerbang NAND kedua serta gerbang NAND ketiga. Mengikut input mereka, ia memberikan output dan pada peringkat akhir dari gerbang NAND, perbezaan output D dan output barrow B akan berada pada keluaran mereka. Perbezaan akhir persamaan output D adalah D = A EquB dan persamaan barrow B sebagai B = A'B. Dengan menggunakan kombinasi gerbang NAND yang berbeza untuk membina separuh-pengurang, persamaan perbezaan dan barrow terakhir adalah D = A⊕B dan B = A'B sahaja. Half Subtractor Terdapat pelbagai aplikasi subtraktor ini. Secara praktikal mereka mudah dianalisis. Sebilangan daripadanya disenaraikan seperti berikut. Untuk mengurangkan nombor yang terdapat pada kedudukan paling sedikit pada lajur, pengurang ini lebih disukai. Unit Aritmetik dan Logik (ALU) yang ada dalam pemproses lebih suka unit ini untuk pengurangan. Untuk mengurangkan gangguan pada suara ini digunakan. Berdasarkan operasi yang diperlukan, setengah pengurang mempunyai keupayaan untuk meningkatkan atau mengurangkan bilangan pengendali. Separuh pengurang digunakan dalam penguat. Semasa menghantar isyarat audio, ini digunakan untuk mengelakkan penyelewengan. Oleh itu, ini semua mengenai Litar pengurangan separuh. Dalam keadaan masa nyata mengurangkan beberapa bilangan bit tidak dapat dilakukan dengan menggunakan separuh pengurang. Kekurangan ini dapat diatasi dengan menggunakan Penolak penuh.

Tinggalkan pesanan

Senarai mesej

Comments Loading ...